#### August, 2002 (Version 1.10)

#### Industry's first complete 32-bit Configurable System-on-Chip (CSoC)

- High-performance, low-power consumption, 32-bit RISC processor (ARM7TDMI™)

- 8Kbyte mixed instruction/data cache

- 16Kbyte internal scratchpad RAM

- Next-generation embedded programmable logic architecture (up to 25,600 ASIC gates)

- High-performance dedicated internal bus (up to 455Mbytes per second at 60 MHz)

- External memory interface supporting Flash, EEPROM, SRAM, and SDRAM

- Advanced real-time, in-system debugging capability

- Stand-alone operation from a single external memory (code + initialization)

- 2.5-volt core with 3.3- or 2.5-volt I/Os

- Four independent high-performance DMA channels

To external memory

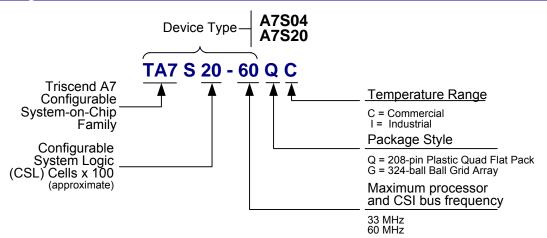

# Triscend A7S Configurable System-on-Chip Platform

#### **Product Description**

- High-performance, 32-bit ARM7TDMI RISC Processor

- Popular, industry-standard 32bit RISC processor

- Binary and source code compatible with other ARM7/ARM7TDMI variants

- Widespread C/C++ compiler, source-level debugger, and RTOS support

- Superior code density using the <u>Thumb</u><sup>®</sup> instruction set

- 54 MIPS (Dhrystone 2.1) at 60 MHz

- Low latency, real-time interrupt response

- Fast hardware multiplier

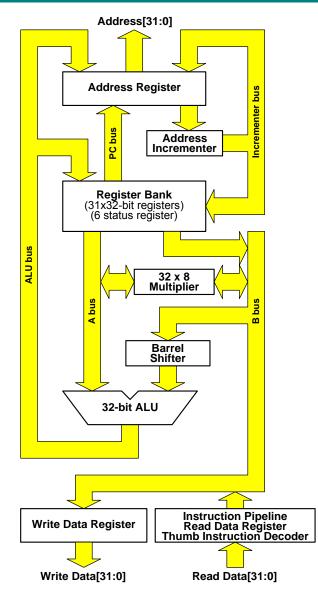

- 32-bit register bank and ALU

- 32-bit addressing 4Gbyte linear address

- 32-bit barrel shifter

- EmbeddedICE™ on-chip debugger

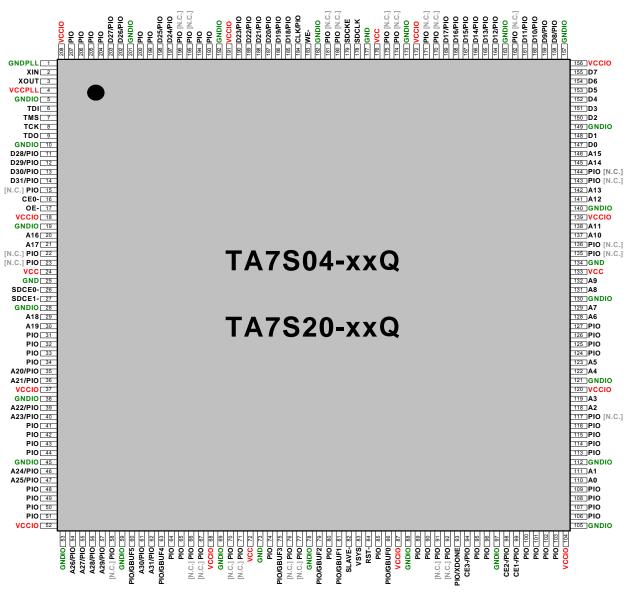

| Device | Embedded<br>Processor<br>Core                                                                     | Dedicated<br>Resources                                                                                                                    | System<br>RAM | Configurable<br>System Logic<br>(CSL) Cells | CSI<br>Address<br>Selectors | PIO*<br>Pins<br>(Max) |

|--------|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------------------------------------|-----------------------------|-----------------------|

| TA7S04 | ARM7TDMI<br>32-bit RISC CPU<br>8K unified cache                                                   | Flash memory interface<br>SDRAM memory interface<br>4-channel DMA controller<br>Two 16C550-style UARTs<br>Two 16-bit timers               | 416-22        | 448                                         | 32                          | 124                   |

| TA7S20 | 8K unified cache<br>Barrel shifter<br>Hardware multiplier<br>Thumb extensions<br>Debug extensions | 32-bit watchdog timer<br>16-input interrupt controller<br>Power management<br>Power-on reset<br>Hardware breakpoint unit<br>JTAG debugger | 4Kx32         | 2,048                                       | 128                         | 252                   |

#### Table 1. Triscend A7S Configurable System-on-Chip Family

\* Maximum PIO on each base device, actual PIO count depends on package style and initialization mode. See Table 61.

#### Rich set of embedded support peripherals

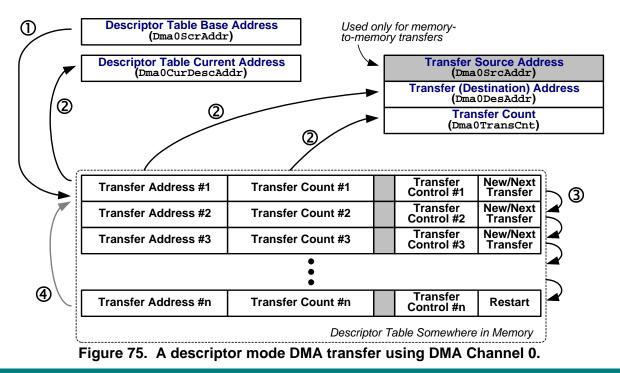

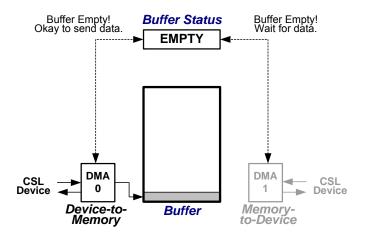

- 4-channel high-performance DMA controller

- fly-by performance

- memory-to-memory transfers

- linked-list DMA

- frame transfer support

- Memory Subsystem Interface Unit (MSSIU) for flexible, glueless interface to external memories (ROM, EEPROM, Flash, SRAM, and SDRAM)

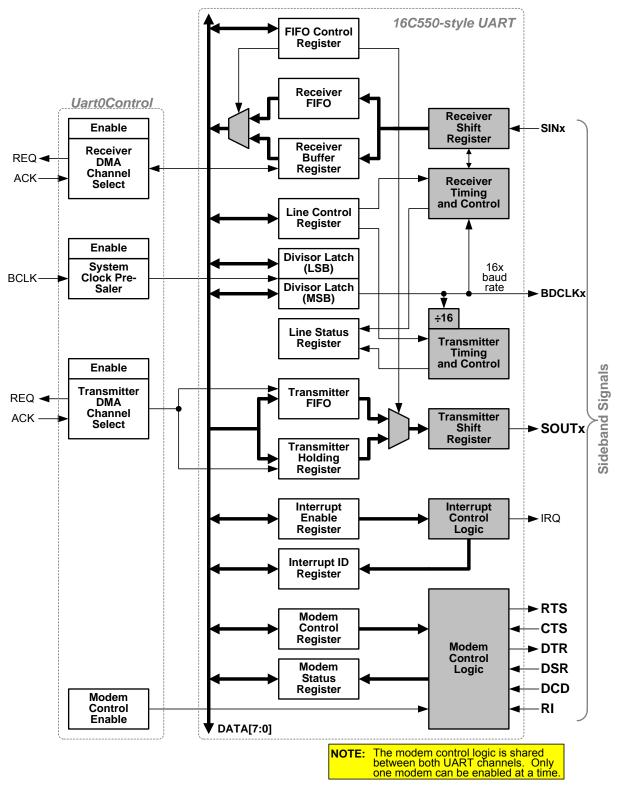

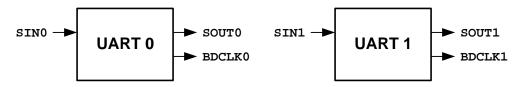

- Two 16C550-style serial ports (UART) with modem interface

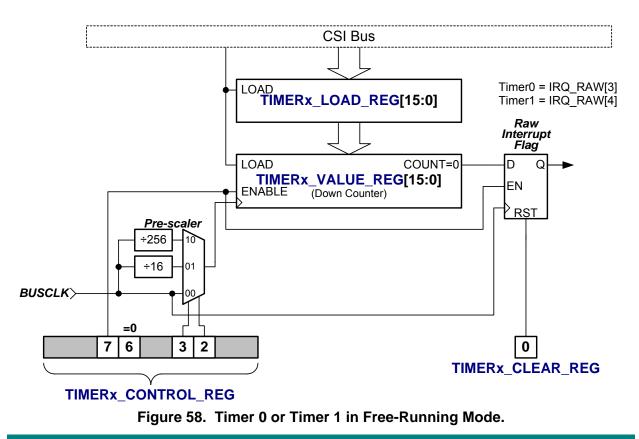

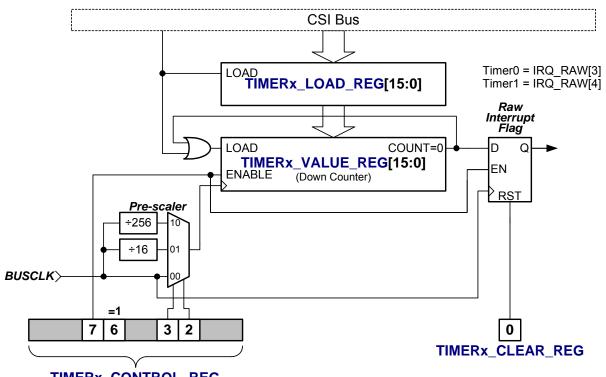

- Two 16-bit timers/counters

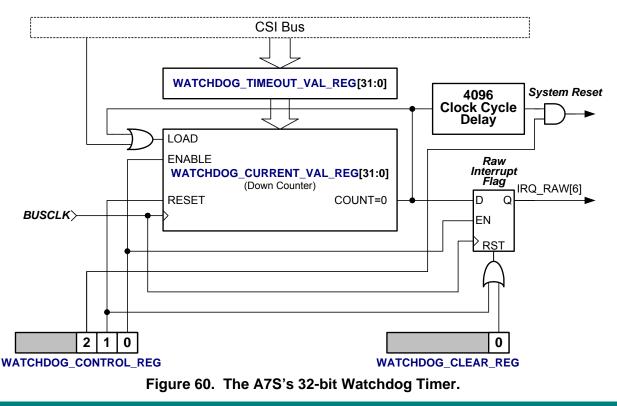

- 32-bit Watchdog timer

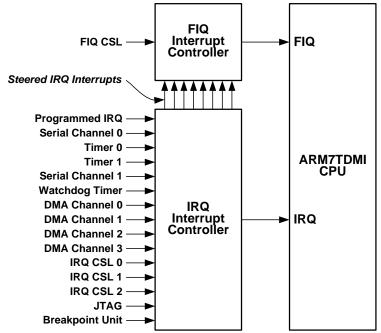

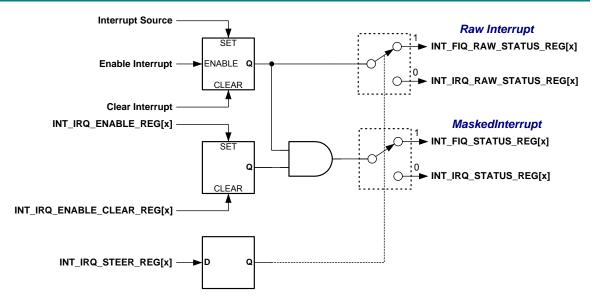

- 16-input interrupt controller with fast interrupt response

- IEEE 1149.1 enhanced JTAG interface

- In-system debug/breakpoint unit

- Power-on reset

- Power-down and power-management modes

#### Full-Featured Memory Interface Unit

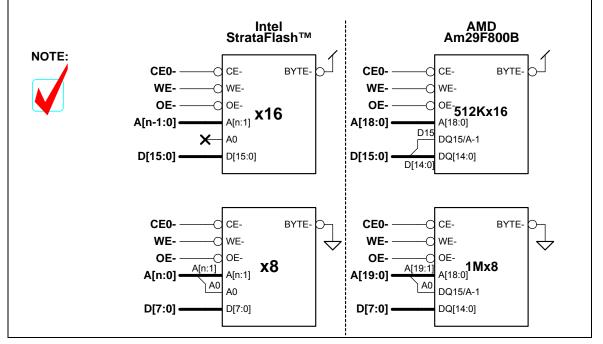

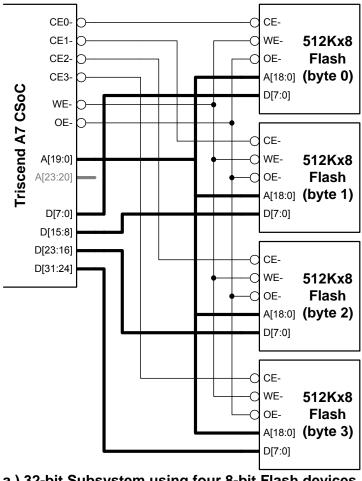

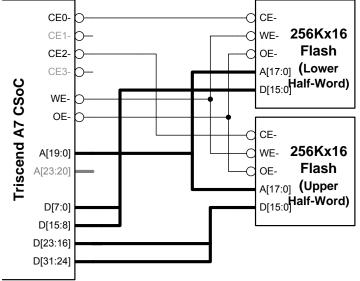

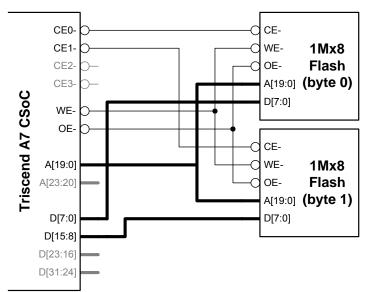

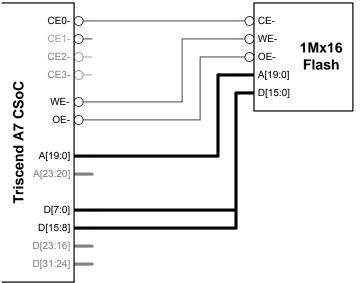

- Simultaneous support for independent external Flash and SDRAM memory subsystems using x8 or x16 memory devices

- Expandable external data bus: 8-bit, 16-bit and 32-bit support

- Up to two external SDRAM banks

- Automatic support for self-refresh, autorefresh and initialization of SDRAM

- Programmable SDRAM parameters for optimal memory bandwidth

# Embedded SRAM-based Configurable System Logic (CSL) matrix

- Next-generation embedded programmable logic architecture, optimized with processor and bus interface

- Over 2,600 flip-flops and 190 programmable inputs and outputs (PIOs)

- Abundant, flexible interconnect structure with easy access to and from system bus

- Dedicated circuitry for fast adders, counters, and multipliers

- CSL cells optionally used as distributed memory, including true dual-port operation

- Six independent low-skew clock or global signal distribution buffers plus bus clock

- Supported by standard logic design tools

- VHDL and Verilog logic synthesis

- Schematic entry

- VHDL and Verilog simulation

- High performance dedicated system bus

- Configurable System Interconnect (CSI) bus integrates CSL matrix, CSoC system

- 455Mbytes per second peak transfer rate

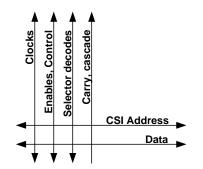

- 32-bit address bus and 32-bit data bus

- Programmable wait-state support

- Openly-defined CSI Socket bus interface to CSL matrix

- CSL peripheral addresses independent of placement in CSL matrix

- CSL peripherals compatible with past and future CSoC families

- Ten bus masters and built-in arbitration

- ARM7TDMI™ CPU

- Four-channel DMA controller

- JTAG interface

### System Overview

The Triscend A7S Configurable System-on-Chip (CSoC) device is a complete, high-performance user-programmable system. The A7S contains

- an embedded 32-bit ARM7TDMI RISC processor

- a next generation embedded programmable logic architecture, optimized for processor and bus interface

- a high-performance 32-bit internal bus supporting up to 455Mbytes per second peak transfer rates

- 16Kbytes of internal scratchpad SRAM memory and a separate 8Kbyte cache.

The ARM7TDMI is a general-purpose 32-bit RISC microprocessor that supports the complete ARM 32-bit instruction set and the reduced 16-bit instruction set, referred to as Thumb. The ARM7TDMI processor offers the following advantages:

- High-performance for very low power consumption and price

- Excellent code density using the Thumb instruction set

- Low-latency interrupt response

#### **ARM7TDMI Processor System with Cache, Scratchpad RAM**

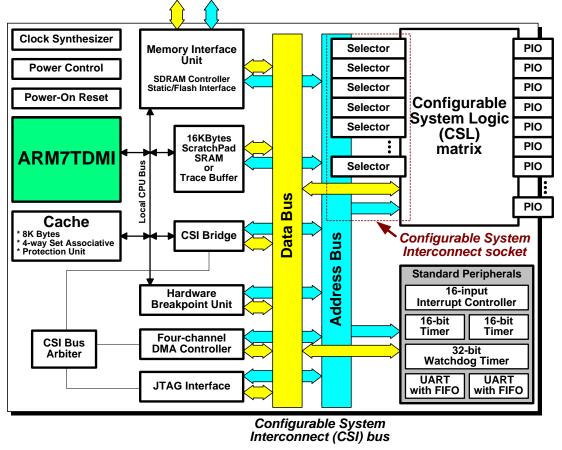

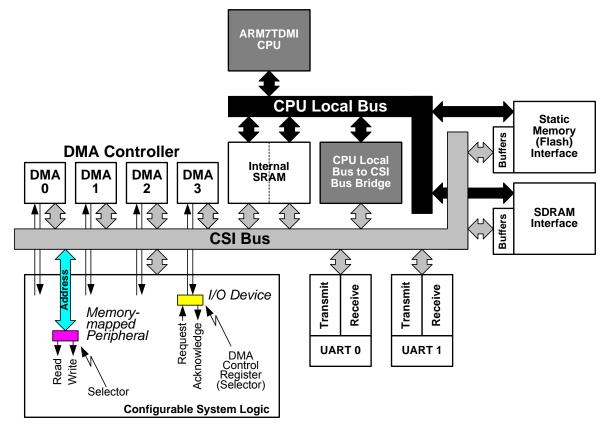

The processor is paired with an 8Kbyte unified code/data cache and a 16Kbyte (4Kx32) scratchpad RAM for storing timing critical code or data. The scratchpad is accessible over the Configurable System Interconnect (CSI) bus by other CSI bus masters, primarily for DMA transfers. The ARM processor is integrated with other system components and the Configurable System Logic (CSL) matrix to provide a complete configurable system, as illustrated in Figure 1.

#### Next-Generation Embedded Programmable Logic Architecture

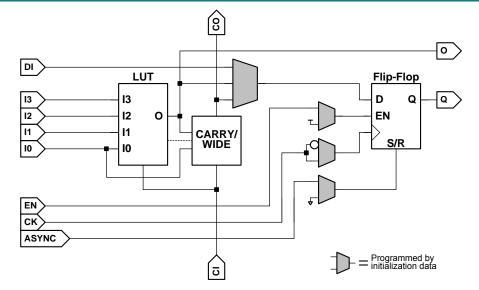

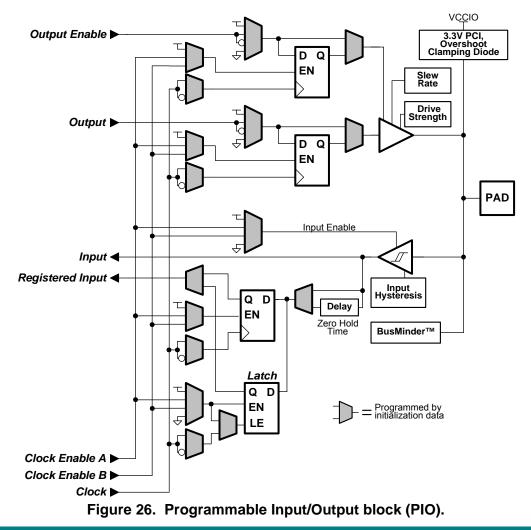

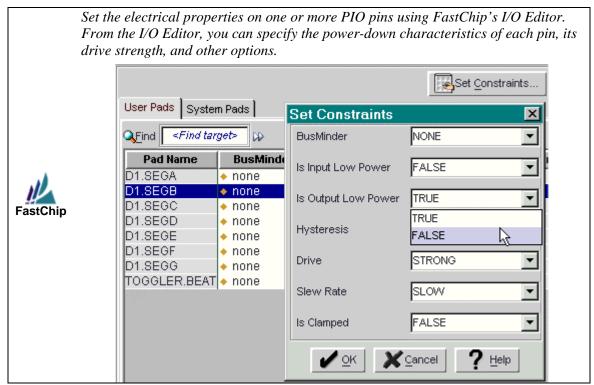

The embedded SRAM-based Configurable System Logic (CSL) matrix provides full, easyto-use system customization. The high-performance programmable logic architecture consists of a highly interconnected matrix of CSL cells. Resources within the matrix provide seamless access to and from the internal CSI bus. Each CSL cell performs various potential functions, including combinatorial and sequential logic. The combinatorial portion performs Boolean logic operations, arithmetic functions, and memory. The sequential element performs independently or in tandem with the combinatorial function. The abundant programmable input/output blocks (PIOs) provide a highly flexible interface between external functions and the internal system bus or configurable system logic. Each PIO offers advanced I/O capabilities including selectable output drive current, optional input hysteresis, and programmable low-power functionality during power-down mode.

#### Internal, High-Performance Bus

A high-performance internal system bus—called the Configurable System Interconnect (CSI) bus— interconnects the embedded processor, its peripherals, and the CSL matrix at a maximum speed of 60MHz. The bus simultaneously provides 32 bits of read data, 32 bits of write data, and a 32-bit address. Multiple bus masters arbitrate for bus access. Potential bus masters include the ARM7TDMI processor, the read and write channels of all four DMA channels, and the JTAG interface. CSL-based devices become CSI bus masters using DMA services. The CSI bus and the local CPU bus following the little endian format.

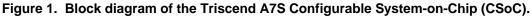

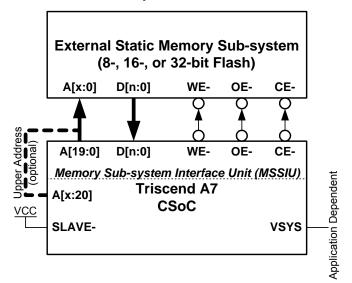

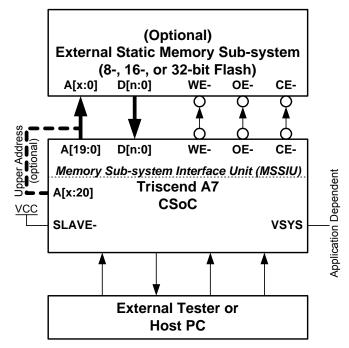

Figure 2. A typical A7S-based system.

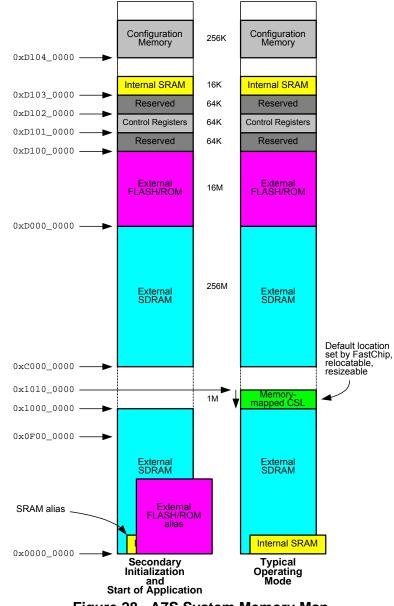

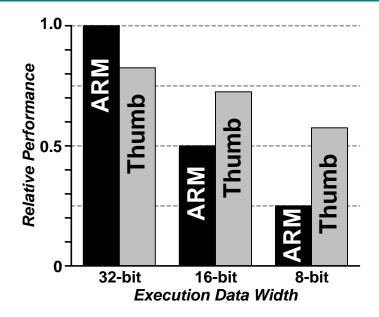

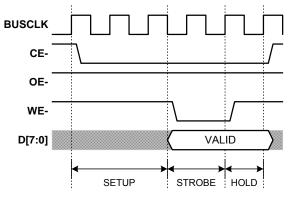

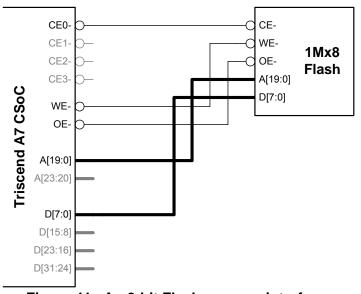

# External Interface to Flash, SDRAM

A static memory interface unit seamlessly connects the A7S device to external static memories such as Flash or SRAM, as shown in <u>Figure 2</u>. An external Flash memory device contains the A7S's initialization boot program plus the system application code. The external memory interface has programmable read/write control and chip-select signals that provide flexible set-up, strobe, and hold timing. The CPU connects directly to external memory, eliminating any potential latency incurred by using the CSI bus. For low frequency or minimal applications, the ARM7TDMI processor directly fetches its instructions from external Flash.

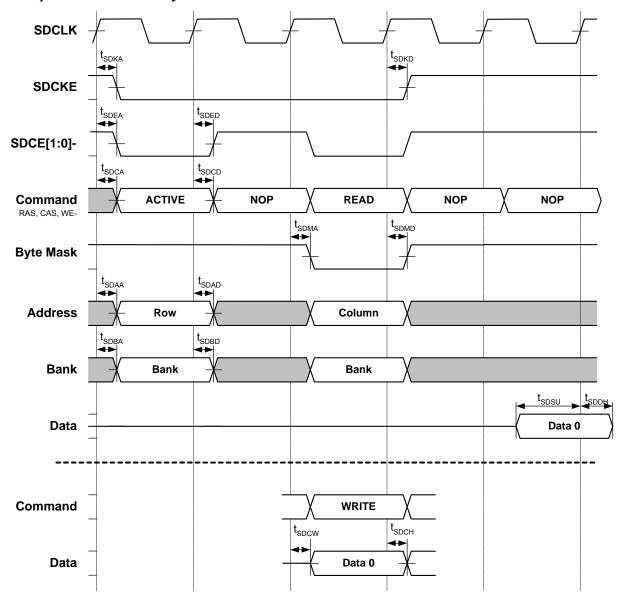

The A7S optionally supports external SDRAM, offering additional affordable and highdensity memory to the system. The SDRAM interface connects an A7S-based system to a variety of SDRAM types and configurations, including 100-pin DIMMs. The SDRAM interface operates at up to 60 MHz and provides options to optimize the interface timing for slower system clocks. SDRAM memory is ideal for DMA buffers. Similarly, the application program can be stored in slow, cheap, byte-wide Flash and copied into SDRAM at power-up. Then, the CPU starts executing code from the wider and faster SDRAM memory. The Flash and SDRAM interfaces share device pins, as shown in Figure 2.

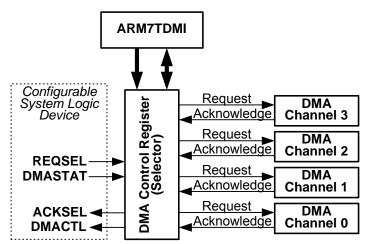

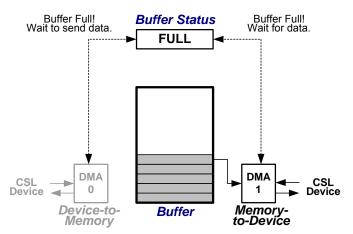

#### **Four-Channel DMA**

The four-channel DMA controller provides high-bandwidth communication between CSLbased I/O devices, at up to 228M bytes per second, per direction. The easy-to-use DMA handshake simplifies interface and control logic within the CSL. The DMA controller provides advanced capabilities such as linked-list and frame-transfer support.

#### **Dedicated Peripherals**

The A7S also offers a set of common dedicated peripherals including

- two 16-bit timers with pre-scalers,

- two 16C450/550-like serial controllers (UART), with an optional modem interface

- a 32-bit watchdog timer, and

- an interrupt controller.

#### **Complete Single-Chip System**

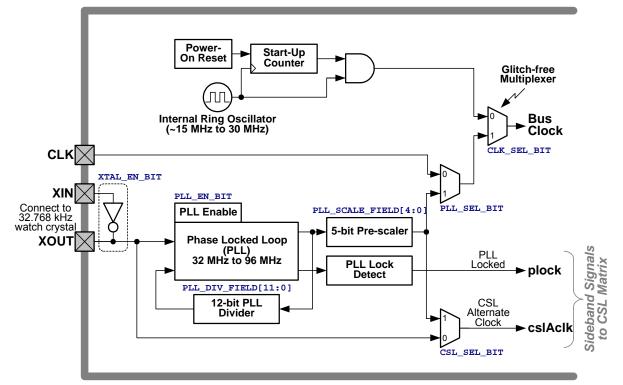

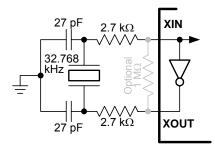

The majority of the system, including the CPU, operates from a single clock signal. The clock source is typically driven directly via an external pin or connected to the on-chip PLL clock synthesizer. The clock synthesizer operates from an external 32.768 kHz watch crystal. Additionally, an internal ring oscillator is provided. Six other global buffers provide high-fanout signals to CSL functions. The bus clock and the global buffers are optionally stopped upon a breakpoint event and shut off during power-down mode.

Power management controls provide selectable power-down options over internal functions. Furthermore, each PIO provides pin-by-pin power-down settings.

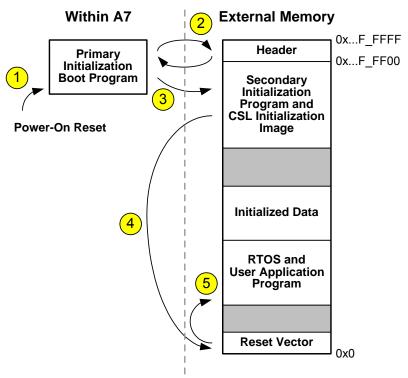

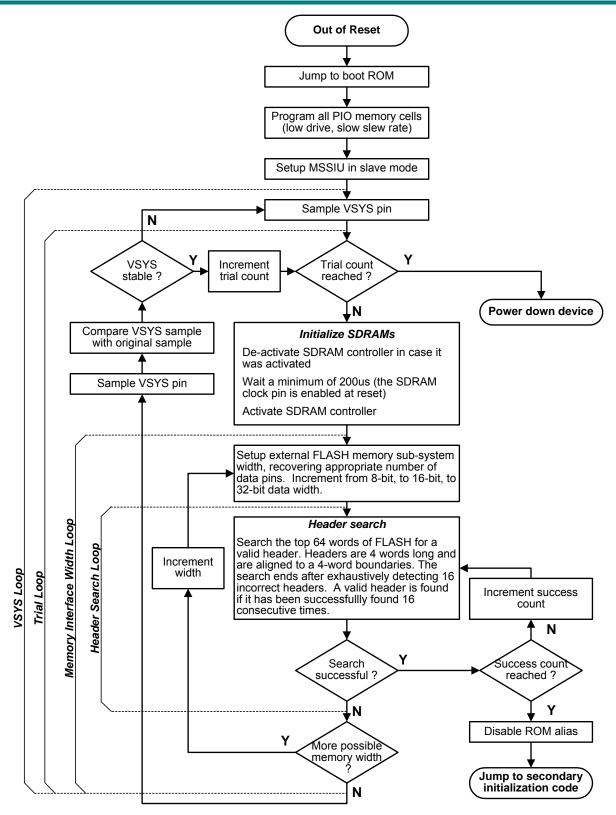

An internal initialization boot ROM controls device initialization after power-on or after the reset pin is released. The initialization boot ROM locates user's initialization data and code stored in external Flash or other non-volatile memory. The Triscend FastChip development system programs external Flash via the A7S's JTAG port.

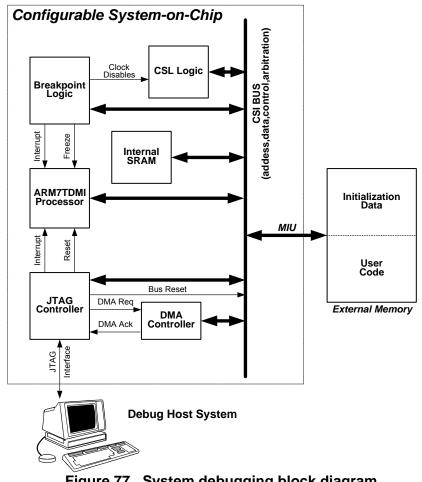

Additionally, the JTAG interface provides real-time, in-system debugging capabilities, eliminating the need for an external emulator. The JTAG interface has full access and control over the CPU, peripherals, and CSL functions during debugging.

When debugging application software, the A7S employs the rich set of standard ARM7TDMI debugging tools. The A7S fully supports the standard ARM internal breakpoint and watchpoint capabilities. In addition, the A7S's breakpoint unit monitors both the CPU local bus or the CSI bus. Upon a predefined set of conditions, the breakpoint unit halts or interrupts the execution of the application program. The breakpoint unit also supports real-time tracing of local CPU bus or the CSI bus transactions.

All together, the Triscend A7S Configurable System-on-Chip (CSoC) platform offers unparalleled time-to-market and performance advantages for embedded system designs.

# A7S Development Support

The Triscend A7S Configurable System-on-Chip (CSoC) platform is supported by a variety of third-party development tools including compilers, debuggers, real-time operating systems (RTOS), and in-system debuggers/emulators as shown in <u>Table 2</u>. Most compilers that support the ARM7 architecture also support the Triscend A7S CSoC device. To accelerate development, there are multiple development boards available, shown in <u>Table 3</u>. Additionally, Triscend provides a free Software Development Kit (SDK) that includes board support packages (BSPs) for leading RTOS environments and a source-level driver library.

The A7S's Configurable System Logic (CSL) matrix is well supported by a variety of logic design entry solutions, including both VHDL or Verilog logic synthesis and schematic entry as shown in <u>Table 2</u>. Likewise, there are VHDL and Verilog simulation models available for popular logic verification tools.

| Table 2. Supported Development Tools for A7S CSoC.                                                          |                                                                                                         |  |  |

|-------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|--|--|

| ARM7TDMI Software Development                                                                               | CSoC/Logic Design Development                                                                           |  |  |

| Triscend Software Development Kit (SDK)                                                                     | Triscend <u>FastChip</u> CSoC Development<br>System                                                     |  |  |

| <ul> <li>Source-level device driver library</li> </ul>                                                      | <ul> <li>Graphical development/integration</li> </ul>                                                   |  |  |

| <ul> <li>Board Support Packages (BSPs)</li> </ul>                                                           | environment, Windows-based                                                                              |  |  |

| Compilers                                                                                                   | Drag-and-drop <u>Soft Module</u> library                                                                |  |  |

| ■ Wind River <u>Diab C/C++™</u> Compiler                                                                    | <ul> <li>Create initialization images for Triscend</li> </ul>                                           |  |  |

| ARM <sup>®</sup> Developer Suite (ADS) C/C++<br>Compiler                                                    | CSoC devices                                                                                            |  |  |

| <ul> <li>GNU C Compiler (<u>GCC</u>)</li> </ul>                                                             | <ul> <li>Download directly or program external<br/>Flash via JTAG</li> </ul>                            |  |  |

| Source-Level Debuggers                                                                                      | <ul> <li>Seamless integration with third-party</li> </ul>                                               |  |  |

| <ul> <li>Wind River <u>visionCLICK</u>, in-system support using Wind River <u>visionPROBE II</u></li> </ul> | <ul><li>microprocessor and logic design tools</li><li>Powerful real-time, in-system debugging</li></ul> |  |  |

| <ul> <li>ARM eXtended Debugger (AXD)</li> </ul>                                                             | VHDL/Verilog Logic Synthesis                                                                            |  |  |

| <ul> <li>GNU <u>gdb</u> Debugger</li> </ul>                                                                 | <ul> <li>Synplicity<sup>®</sup> Synplify<sup>®</sup></li> </ul>                                         |  |  |

| Real-Time Operating System (RTOS)                                                                           | <ul> <li>Synopsys<sup>®</sup> FPGA Compiler II</li> </ul>                                               |  |  |

| Support                                                                                                     | Schematic Entry                                                                                         |  |  |

| Wind River Tornado/ <u>VxWorks®</u>                                                                         | <ul> <li>Cadence/<u>OrCAD Capture</u></li> </ul>                                                        |  |  |

| ■ Red Hat <u>eCos™</u>                                                                                      | <ul> <li>SpinCircuit <u>eCapture</u></li> </ul>                                                         |  |  |

| <ul> <li>Red Hat <u>µClinux</u></li> </ul>                                                                  | Innoveda <u>ViewDraw</u>                                                                                |  |  |

| JTAG-Based Hardware<br>Emulators/Debuggers                                                                  | VHDL Logic Simulation                                                                                   |  |  |

| <ul> <li>Wind River visionPROBE II (ARM and</li> </ul>                                                      | ■ Model Technology <sup>™</sup> ModelSim                                                                |  |  |

| CSoC debugging)                                                                                             | Innoveda <u>Fusion/Speedwave</u>                                                                        |  |  |

| <ul> <li>ARM Mutli-ICE<sup>™</sup> (ARM only debugging)</li> </ul>                                          | <ul> <li>VITAL/SDF support</li> </ul>                                                                   |  |  |

| EPI <u>JEENI</u> and <u>MAJIC</u> <sup>™</sup> (ARM only de-                                                | Verilog Logic Simulation                                                                                |  |  |

| bugging)                                                                                                    | ■ Model Technology <sup>™</sup> ModelSim                                                                |  |  |

|                                                                                                             | Cadence <sup>®</sup> <u>Verilog XL<sup>®</sup></u>                                                      |  |  |

|                                                                                                             | ■ Synopsys <sup>®</sup> <u>VCS</u>                                                                      |  |  |

|                                                                                                             |                                                                                                         |  |  |

Triscend CSI Bus Functional Model

| Table 3. A7S Development Boards | - |

|---------------------------------|---|

|---------------------------------|---|

| Supplier                        | Part Number        |

|---------------------------------|--------------------|

| Triscend Corporation            | <u>THW-KIT-720</u> |

| Embedded Performance Inc. (EPI) | Dev-A7             |

### PC-Based Development Platform

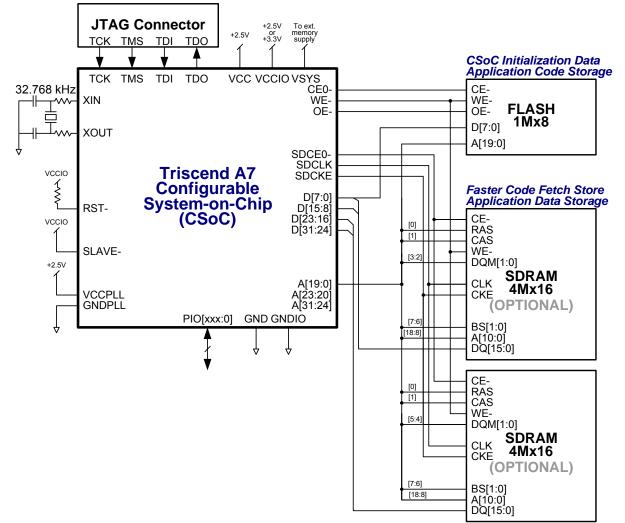

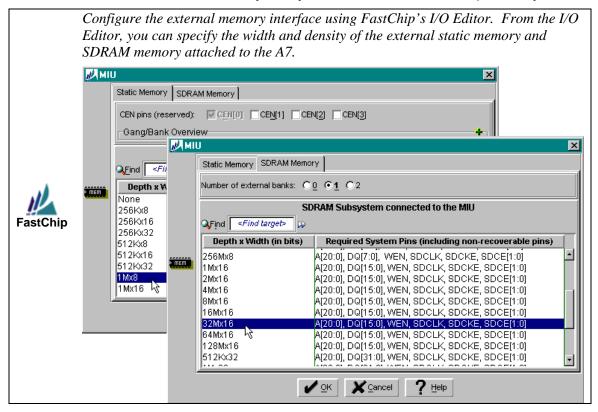

<u>Figure 3</u> presents a detailed view of the entire Triscend A7S development flow. FastChip is a Windows-based application and operates on most PC-compatible computers with the recommended minimum 192Mbytes of RAM memory. The Triscend FastChip development system provides design integration and configuration capabilities, working in conjunction with third-party logic design and software development tools.

#### Powerful FastChip CSoC Development System

FastChip includes a powerful <u>Soft Module library</u> of commonly used embedded systems functions like additional UARTs, timers, various bus interfaces, etc. Likewise, FastChip includes libraries that allow designers to create custom functions using third-part logic design and simulation tools. Designs imported into FastChip via an EDIF 2.0.0 netlist become FastChip modules.

FastChip also exports a CSoC designs for either VHDL or Verilog logic simulation purposes. A Triscend-provided bus functional model simulates traffic on the A7S's internal CSI bus.

#### Seamless Integration with ARM7TDMI Compiler

After defining the A7S's logic, FastChip's Bind utility creates the physical hardware implementation for the CSoC device. Similarly, FastChip's Generate utility allocates addresses for any functions attached to the Configurable System Interconnect (CSI) bus and creates an application programming model for a third-party ARM compiler. This model includes register definitions for both standard ARM7TDMI functions and any custom hardware.

FastChip combines the output from the Bind utility and the object code from the ARM7TDMI compiler to create a CSoC initialization image. Using this image, FastChip either directly downloads to an A7S device or programs external Flash memory attached to the A7. Optionally, the initialization image can be saved as an Intel Hex file four use with an external device programmer.

#### Real-time, In-system, Full-Speed Debugging

Furthermore, FastChip provides a real-time, in-system debugging environment using the actual A7S production silicon with the actual system hardware and application software. FastChip drives a supported JTAG-based debugger/emulator and provides interfaces to third-party source-level debuggers. Via a source-level debugger, software developers have register-level access to the A7S device, complete with breakpoints and trace. Fast-Chip's Debug utility also provides logic debugging capabilities, including the ability to probe flip-flop values and the outputs of CSL cells.

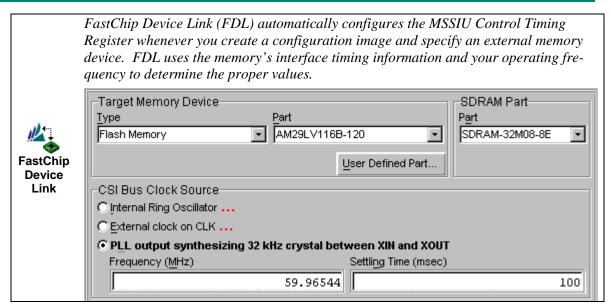

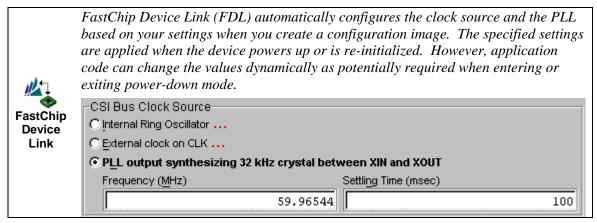

FastChip's Configure and Download/Debug utilities are packaged as a separate, standalone application called FastChip Device Link (FDL), providing software developers with necessary software development capabilities without the complexity of the entire FastChip CSoC development system.

## **Comprehensive Technical Support**

The Triscend A7S Configurable System-on-Chip family and the FastChip development system are supported by a world-wide network of factory-trained field applications engineers. Additionally, the Triscend SupportCenter provides online support via the world-wide web at <a href="http://support.triscend.com">http://support.triscend.com</a> or via E-mail at <a href="http://supportCenter@Triscend.com">SupportCenter@Triscend.com</a>.

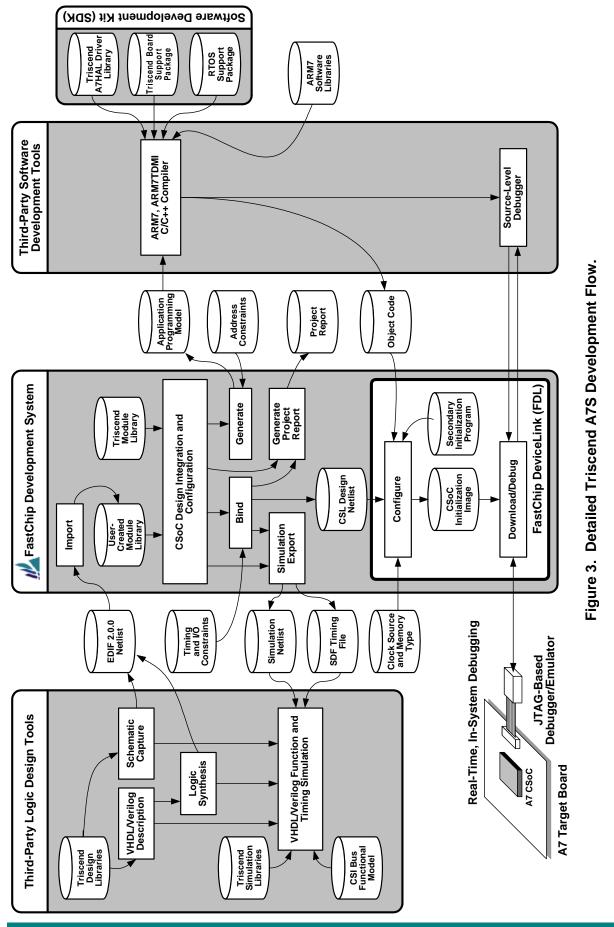

Figure 4. ARM7TDMI CPU Block Diagram.

# **ARM7TDMI Processor Overview**

The A7S Configurable System-on-Chip family includes an embedded ARM7TDMI 32-bit RISC processor. The A7S is binary compatible with other ARM7-based devices. Figure 4 shows the major architectural features within the ARM7TDMI processor and the following text provides a brief overview. Please refer to the <u>ARM7TDMI data sheet</u> or <u>Resources</u> for more additional information.

# Notable Architectural Features

# Registers

The ARM7TDMI CPU has sixteen active 32-bit general-purpose registers at any given instance. There are a total of 31 such registers but some are only available during exception handling.

# Arithmetic Logic Unit

The arithmetic logic unit (ALU) performs 32-bit arithmetic and logic instructions in a single clock cycle.

### **Barrel Shifter**

The 32-bit barrel shifter allows a general shift operation to be combined with a general ALU operation in a single instruction that executes in a single clock cycle.

#### Hardware Multiplier

The ARM7TDMI processor includes a dedicated 32 x 8 hardware multiplier. Additionally, the multiplier supports multiply-accumulate functions, which are central to many digital signal processing (DSP) applications.

The performance of the multiplier depends on the data values and the type of data multiplied, as shown in <u>Table 4</u>. The multiplier terminates the instruction immediately upon computing the result, regardless of the data width.

| Multiplier Operation                                                      | Clock Cycles |  |  |  |

|---------------------------------------------------------------------------|--------------|--|--|--|

| 32 x 32 = 32                                                              | 2 to 5       |  |  |  |

| Multiply two 32-bit values with a 32-bit result                           |              |  |  |  |

| 32 x 32 = 64                                                              | 3 to 6       |  |  |  |

| Multiply two 32-bit values with a 64-bit result                           |              |  |  |  |

| 32 x 32 + 32 = 32                                                         | 3 to 6       |  |  |  |

| Multiply two 32-bit values, add the result with a 32-bit value, producing |              |  |  |  |

| a 32-bit result                                                           |              |  |  |  |

| 32 x 32 + 64 = 64                                                         | 4 to 7       |  |  |  |

| Multiply two 32-bit values, add the result with a 64-bit value, producing |              |  |  |  |

| a 64-bit result                                                           |              |  |  |  |

#### Table 4. ARM7TDMI Multiplier Performance.

# **Conditional Code Execution**

Each ARM instruction is conditionally executed, based on the current status flags. The capability minimizes short branches, which might otherwise reduce system performance.

#### **Three-Address Data Processing Instructions**

The two source operand registers and the result register are independently specified, which aids performance and improves code density.

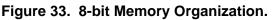

#### Thumb Instruction Set

The Thumb instruction set provides an extremely dense 16-bit representation of the most commonly used instructions. Thumb offers cost advantages for smaller systems and performance advantages in systems with 8-bit or 16-bit external memory subsystems.

#### **CISC-like Instructions**

Load and store multiple instructs allow an application to quickly and easily save and restore registers

# **Operating States**

The ARM7TDMI processor provides two operating states. <u>ARM state</u> executes 32-bit, word-aligned ARM instructions, providing the full richness of the ARM instruction set. The alternate <u>THUMB state</u> operates with 16-bit, half-word aligned THUMB instructions, offering significant code size reductions. An application can switch between the two states providing the optimum mix of performance and code density.

### **Operating Modes**

The ARM7TDMI processor supports seven different operating modes, as shown in <u>Table</u> <u>5</u>. Mode changes may occur under software control or by external interrupts or exception processing. Most application programs execute in User mode. The non-user modes, known as privileged modes, are designed to service interrupts or exceptions, or to access protected system resources.

| Mode             | Purpose                                                   |

|------------------|-----------------------------------------------------------|

| User (usr)       | The normal ARM program execution state.                   |

| FIQ (fiq)        | Designed to support a data transfer or channel processes. |

| IRQ (irq)        | Used for general-purpose interrupt handling.              |

| Supervisor (svc) | Protected mode for the operating system.                  |

| Abort (abt)      | Entered after a data or instruction prefetch abort.       |

| System (sys)     | A privileged user mode for the operating system.          |

| Undefined (und)  | Entered when an undefined instruction is executed.        |

Table 5. ARM7TDMI Operating Modes.

### Registers

The ARM7TDMI has 37 registers, consisting of 31 general-purpose 32-bit registers and six status registers. However, not all registers are viewable at once. The visibility of a particular register depends on the processor state and operating mode.

#### ARM State Register Set

In ARM state, 16 general registers and one or two status registers are visible at any one time. In privileged (non-user) mode, various mode-specific banked registers become available. <u>Table 6</u> shows which registers are available in each operating mode. Banked registers are shaded.

The ARM state register set contains 16 directly accessible registers, named R0 through R15. All of these, except R15, are general-purpose registers and may store either data or address values.

Additionally, there is a seventeenth register used to store status information, named CPSR (Current *Program Status Register*).

FIQ mode supports seven banked registers mapped to R8 through R14 (R8\_fiq through R14\_fiq). In ARM state, many FIQ handlers do not need to save any registers. User, IRQ, Supervisor, Abort, and Undefined each have two banked registers mapped to R13 and R14, allowing each of these modes to have a private stack pointer and link registers.

- **R14** Used as the subroutine link register. Receives a copy of R15 when the Branch and Link (BL) instruction is executed. At all other times, R14 performs as a general-purpose register. Similarly, the corresponding banked registers— R14\_svc, R14\_irq, R14\_fiq, R14\_abt, and R14\_und—hold the return values of R15 when interrupts or exceptions occur, or when a Branch and Link (BL) instruction is executed within an interrupt or exception handling routine.

- R15 Holds the Program Counter (PC). In ARM state, R15 bits [1:0] are zero while R15 bits [31:2] contain the program counter (PC). In THUMB state, R15 bit 0 is zero and R15 bits [31:1] contain the PC.

- **CPSR** The Current <u>*Program Status Registers*</u> (CPSR) contains condition code flags and the current mode bits.

### ARM Thumb Extensions

The ARM7TDMI processor includes the Thumb extension to the 32-bit ARM architecture. The Thumb instruction set features a subset of the most commonly used 32-bit ARM instructions, which have been compressed into 16-bit wide op codes. When executed, these 16-bit instructions are decompressed transparently into full 32-bit ARM instructions, in real time, without degrading performance.

Designers can use both 16-bit Thumb and 32-bit ARM instructions sets in an application, providing an optimal mix of code density, performance, and instruction richness.

| System & | FIO      | C          | A la a ut |          | l lu defined |

|----------|----------|------------|-----------|----------|--------------|

| User     | FIQ      | Supervisor | Abort     | IRQ      | Undefined    |

| R0       | R0       | R0         | R0        | R0       | R0           |

| R1       | R1       | R1         | R1        | R1       | R1           |

| R2       | R2       | R2         | R2        | R2       | R2           |

| R3       | R3       | R3         | R3        | R3       | R3           |

| R4       | R4       | R4         | R4        | R4       | R4           |

| R5       | R5       | R5         | R5        | R5       | R5           |

| R6       | R6       | R6         | R6        | R6       | R6           |

| R7       | R7       | R7         | R7        | R7       | R7           |

| R8       | R8_fiq   | R8         | R8        | R8       | R8           |

| R9       | R9_fiq   | R9         | R9        | R9       | R9           |

| R10      | R10_fiq  | R10        | R10       | R10      | R10          |

| R11      | R11_fiq  | R11        | R11       | R11      | R11          |

| R12      | R12_fiq  | R12        | R12       | R12      | R12          |

| R13      | R13_fiq  | R13_svc    | R13_abt   | R13_irq  | R13_und      |

| R14      | R14_fiq  | R14_svc    | R14_abt   | R14_irq  | R14_und      |

| R15 (PC) | R15 (PC) | R15 (PC)   | R15 (PC)  | R15 (PC) | R15 (PC)     |

# Table 6. Register organization in ARM state.

#### ARM State General Registers and Program Counter

#### ARM State Program Status Registers

| CPSR | CPSR     | CPSR     | CPSR     | CPSR     | CPSR     |

|------|----------|----------|----------|----------|----------|

|      | SPSR_fiq | SPSR_svc | SPSR_abt | SPSR_irq | SPSR_und |

indicates a banked register.

Thumb offers better code density than common 8- and 16-bit CISC/RISC controllers. Thumb application programs are merely a fraction of the code size of traditional 32-bit architectures. Consequently, program memory is smaller and hence cost reduced.

#### THUMB State Register Set

The THUMB state register set is a subset of the ARM state set. The programmer has direct access to eight general-purpose registers, named R0 through R7, plus the Program Counter (PC), a stack pointer register (SP), a link register (LR), and the Current Program Status Register (CPSR).

There are banked Stack Pointers, Link Registers, and Saved Process Status Registers (SPRs) for each privileged mode, as shown in <u>Table 7</u>.

In THUMB state, registers R8 through R15—called the Hi registers—are not part of the standard THUMB register set. However, the assembly-language programmer has limited access to the Hi registers and can use them for fast temporary storage.

Values are transferred from a Lo register (R0 through R8) to a Hi register, and *vice versa*, using special variants of the MOV instruction. Hi register values can also be compared against or added to Lo register values using the CMP and ADD instructions.

#### **Program Status Registers**

The ARM7TDMI processor contains a Current <u>**Program Status Register</u>** (CPSR) plus five Saved Program Status Registers (SPSRs) used by exception handlers. These registers</u>

- Hold information about the most recently-performed ALU operation

- Control the enabling and disabling of interrupts

- Set the processor operating mode

The bottom 8 bits of a program status register, consisting of the I, F, T, and M[4:0] bits, are known collectively as the control bits. These bits change when an exception occurs.

| User | FIQ                                  | Supervisor | Abort    | IRQ      | Undefined |

|------|--------------------------------------|------------|----------|----------|-----------|

| R0   | R0                                   | R0         | R0       | R0       | R0        |

| R1   | R1                                   | R1         | R1       | R1       | R1        |

| R2   | R2                                   | R2         | R2       | R2       | R2        |

| R3   | R3                                   | R3         | R3       | R3       | R3        |

| R4   | R4                                   | R4         | R4       | R4       | R4        |

| R5   | R5                                   | R5         | R5       | R5       | R5        |

| R6   | R6                                   | R6         | R6       | R6       | R6        |

| R7   | R7                                   | R7         | R7       | R7       | R7        |

| SP   | SP_fiq                               | SP_svc     | SP_abt   | SP_irq   | SP_und    |

| LR   | LR_fiq                               | LR_svc     | LR_abt   | LR_irq   | LR_und    |

| PC   | PC                                   | PC         | PC       | PC       | PC        |

|      | THUMB State Program Status Registers |            |          |          |           |

| CPSR | CPSR                                 | CPSR       | CPSR     | CPSR     | CPSR      |

|      | SPSR_fiq                             | SPSR_svc   | SPSR_abt | SPSR_irq | SPSR_und  |

# Table 7. Register organization in THUMB state. THUMB State General Registers and Program Counter

indicates a banked register.

Suctom 9

If the processor is operating in a privileged mode, these bits may be manipulated by software.

When changing a program status register value, you must ensure that the reserved bits are not altered. Furthermore, the application program should not rely on the reserved bits containing a specific value.

| Bit  | Description/Function                                                              |

|------|-----------------------------------------------------------------------------------|

| 31   | Negative, Less Than (N):                                                          |

| 30   | Zero (Z):                                                                         |

| 29   | Carry, Borrow, or Extend (C):                                                     |

| 28   | Overflow (V):                                                                     |

| 27:8 | Reserved                                                                          |

| 7    | IRQ Disable (I):                                                                  |

|      | 0: IRQs enabled                                                                   |

|      | 1: IRQs disabled                                                                  |

| 6    | FIQ Disable (F):                                                                  |

|      | 0: FIQs enabled                                                                   |

|      | 1: FIQs disabled                                                                  |

| 5    | THUMB State Enable (T):                                                           |

|      | 0: Operating in <u>ARM state</u> , using 32-bit instructions                      |

|      | 1: Operating in <u>THUMB state</u> , using 16-bit instructions                    |

| 4:0  | Operating Mode (M[4:0]):                                                          |

|      | These bits determine the processor's operating mode, as shown in <u>Table 8</u> . |

|      | Only use values explicitly defined. These values are typically set by the real-   |

|      | time operating system.                                                            |

### Program Status Register Format

| roccssor operating mode |        |  |  |

|-------------------------|--------|--|--|

| Mode                    | M[4:0] |  |  |

| User                    | 10000  |  |  |

| FIQ                     | 10001  |  |  |

| IRQ                     | 10010  |  |  |

| Supervisor              | 10011  |  |  |

| Abort                   | 10111  |  |  |

| Undefined               | 11011  |  |  |

| System                  | 11111  |  |  |

#### Table 8. Processor Operating Mode Settings.

# **Exception Vectors**

When an exception occurs, such as a reset or an interrupt, the processor branches to a predefined vector address as shown in <u>Table 9</u>. The table shows the source or cause of the exception, the priority of each exception should they happen simultaneously, the CPU operating state entered by the exception, and the vector address.

| Exception                |          |                                                                              | CPU        | Vector  |

|--------------------------|----------|------------------------------------------------------------------------------|------------|---------|

| Туре                     | Priority | Cause/Source                                                                 | State      | Address |

| Fast Interrupt<br>(FIQ)  | 3        | FIQ interrupt to the Interrupt<br>Controller                                 | FIQ        | 0x1C    |

| Interrupt<br>(IRQ)       | 4        | Any of the 15 IRQ interrupts to the Interrupt Controller                     | IRQ        | 0x18    |

| Reserved                 |          |                                                                              |            | 0x14    |

| Data Abort               | 2        | Memory access violations from<br>the Protection Unit                         | Abort      | 0x10    |

| Prefetch<br>Abort        | 5        | The CPU attempts to execute an invalid instruction or a BKPT instruction     | Abort      | 0x0C    |

| Software<br>Interrupt    | 6        | The CPU executes a swi<br>instruction                                        | Supervisor | 0x08    |

| Undefined<br>Instruction | 6        | The CPU executes a coprocessor<br>instruction and no coprocessor<br>responds | Undefined  | 0x04    |

| Reset                    | 1        | Any reset condition                                                          | Supervisor | 0x00    |

#### Table 9. ARM7TDMI Exception Types and Vectors.

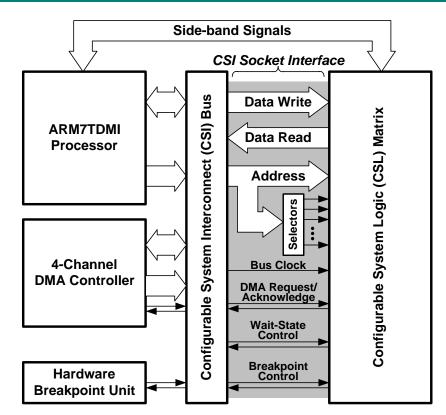

# Figure 5. The Configurable System Interconnect (CSI) bus and the socket interface to user-defined logic functions in the CSL matrix.

# Configurable System Interconnect (CSI) Bus

The Configurable System Interconnect (CSI) bus, shown in <u>Figure 5</u>, bridges the processor with its peripherals including the Configurable System Logic (CSL) matrix.

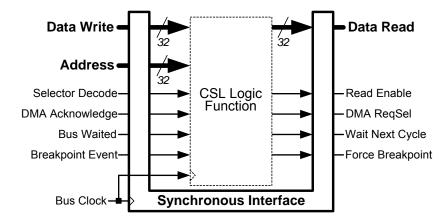

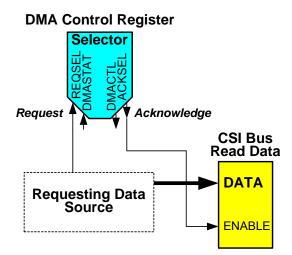

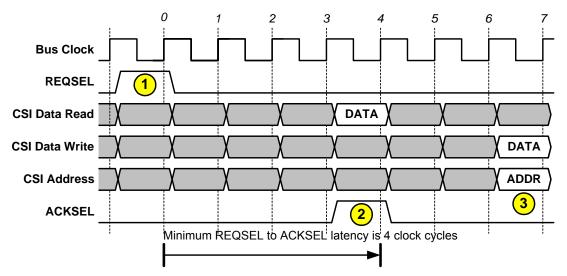

The CSI bus socket provides a simple, synchronous interface to custom logic functions or peripherals implemented in the CSL matrix, as shown in <u>Figure 6</u>. The CSI bus interface socket consists of the following signals.

- A 32-bit write data port

- A 32-bit read data port, including a read enable signal and read return path from the CSL matrix onto the CSI system bus

- A 32-bit address port

- A set of address Selector functions to decode CSI bus transactions. The number of Selectors varies according to device size as shown in <u>Table 10</u>. The Selectors also optionally steer DMA request and acknowledge signals to and from CSL-based devices.

- The bus clock. All CSI bus events occur on the rising edge of the bus clock.

- Wait-state control and monitor signals

- Hardware breakpoint control and monitor signals

#### **Data Write Port**

After being granted the bus by the CSI bus arbiter, the current CSI bus master presents up to 32 bits of write data on the CSI socket during every active bus cycle.

#### Figure 6. The CSI bus socket represents a simple-to-use, synchronous interface to custom logic functions implemented in the CSL logic matrix.

### Data Read Port

An decoded or acknowledged CSL-based function asserts its read enable signal to present up to 32 bits of read data onto the CSI bus socket. All unselected CSL functions drive the read port with logic Low. The read data values from all CSL-based functions are logically OR-ed together before appearing on the CSI bus. Read data can be presented during every active bus cycle.

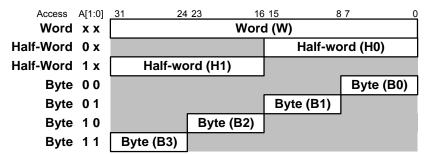

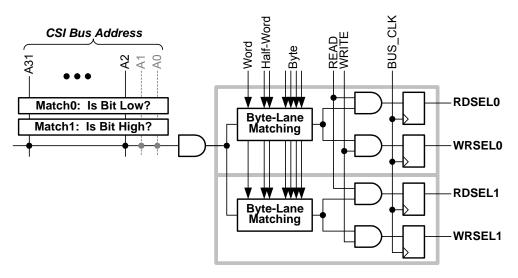

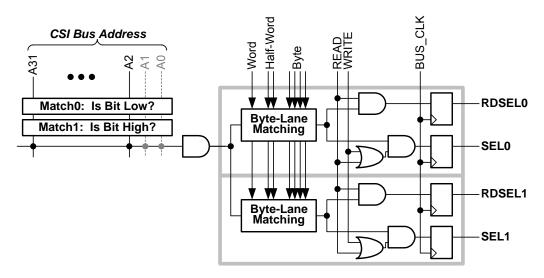

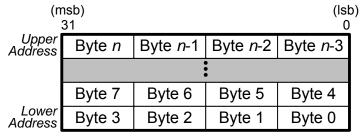

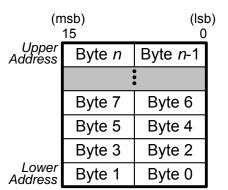

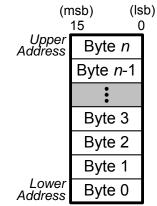

### Byte, Half-Word, and Word Operations and Data Alignment

The CSI bus provides automatic handling for byte, half-word, and word operations. <u>Figure</u> <u>7</u> shows the supported data types and the associated byte lane alignment for each type. A 32-bit register can optionally be addressed as a single 32-bit word, two 16-bit half-words, or as four individual bytes.

#### Address Port

The bus master, granted the bus by the CSI bus arbiter, presents 32 bits of address on the CSI socket during every active bus cycle.

All 32 address bits appear the CSI interface socket. Typically, only a few if any of the address signals are used by functions in the CSL matrix. The actual address decoding for a bus transaction is usually performed using the on-chip address Selectors.

#### Address Selectors

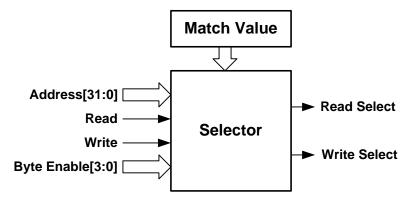

The CSI socket interface practically eliminates the need to use any CSL matrix resources to decode bus transactions. One of the more important elements in the CSI socket interface is the programmable address decoder function, generically called a Selector. A Selector performs functions similar to a chip-select unit or an address decoder built using a PLD. As shown in Figure 8, a Selector decodes a range of addresses and produces separate read and write decode outputs, based on the bus address, and the size of the data transaction, commonly referred to as byte enables. By specifying the matching conditions, a Selector decodes a range of addresses, stretching from a single byte up to a 4Gbyte region in memory.

Figure 8. A simplified view of a Selector.

# Address Selector Operation

A Selector detects transactions to a specified range of CSI bus addresses by decoding the full 32-bit CSI address bus. If a transaction targets its address range, the Selector asserts one of its read or write decode outputs coincident with the appearance of address and data on the bus socket, all synchronized to the bus clock. This approach dramatically simplifies the logic and timing of CSL logic functions attached to the CSI bus.

The number of available Selectors depends on the particular device. The number of Selectors grows with the increasing size of the CSL matrix. There is one Selector located above every column of sixteen CSL cells in a bank, as shown in <u>Table 10</u> and <u>Figure 16</u>.

| Table | 10. | Number | of | selectors | by | / 0 | levice. |

|-------|-----|--------|----|-----------|----|-----|---------|

|       |     |        |    |           |    |     |         |

| Device | Selectors |  |  |

|--------|-----------|--|--|

| TA7S04 | 32        |  |  |

| TA7S20 | 128       |  |  |

Functionally, each Selector is similar to diagram shown in Figure 9. Each Selector contains two 32-bit registers that define the target address. The MATCH0 register defines which particular address bits match when the address bit is Low. The MATCH1 register defines which particular address bits match when the address bit is High. If the same bit location is set in both registers, then the corresponding address bit is a "don't care", matching regardless if the address bit is High or Low. For the A7, bits A[1:0] are typically programmed for "don't care" because most transactions are word-oriented and word aligned.

If all the address bits match the values defined in the MATCH0 and MATCH1 register, then the Selector further decodes read or write operations and the byte-lane alignment setting. During a read operation, if the address matches to the correct target address and

byte-lane alignment, then the Selector asserts its read-select output, RDSEL. Likewise, if the transfer is a write, then the Selector asserts its write-select output, WRSEL.

### **Address Specification**

The MATCH0 and MATCH1 register values are automatically defined by the Triscend FastChip development system at design time and are loaded into the Selectors during device initialization. These register values are not changed by application software.

The addresses loaded into MATCH0 and MATCH1 registers and the byte-lane alignment are symbolically defined during hardware design by defining the following parameters.

- The symbolic name for the address range. This is the name used in application software to refer to the target address range.

- The size of the addressed range, which must be a power of two, ranging from '1' indicating a single byte to '4G' indicating a 4G byte region.

- The byte alignment for the selector, whether defined a word-wide, half-word-wide, or byte-wide access.

- The address space or spaces to which the selector should respond. For the A7, there is a single 32-bit linear data space.

The Triscend FastChip Development System allows you to specify only a **symbolic** address. The FastChip Generate utility allocates and assigns the physical address for you, based on the resource requirements that you define. The Generate utility also passes the symbolic and physical assignments to your compiler via a header file. By assigning only a symbolic address, all of your functions are re-useable and can be mixed and matched without address conflicts.

Figure 9. The distributed address selector functions decode read and write transactions to a target address range. The Selectors eliminate the need to build decoding logic using CSL resources.

# Figure 10. In chip select mode, an address selector decodes any read or write transaction to the target address range.

The Triscend FastChip development system examines these settings from all of the Selectors defined in the hardware design. It then allocates physical addresses to each Selector. The assigned addresses are defined and specified in a header file, used during software development.

#### **Address Selector Modes**

A Selector performs one of three potential functions as shown in <u>Table 11</u>.

| Table 11. Address Selector Types. |                  |                               |  |  |  |  |

|-----------------------------------|------------------|-------------------------------|--|--|--|--|

| Selector Modes                    | Ports            | Function                      |  |  |  |  |

| Selector                          | RDSEL0<br>RDSEL1 | Read decode                   |  |  |  |  |

|                                   | WRSEL0<br>WRSEL1 | Write decode                  |  |  |  |  |

| Chip Select                       | RDSEL0<br>RDSEL1 | R/W- control                  |  |  |  |  |

| Chip Select                       | SEL0<br>SEL1     | Chip select                   |  |  |  |  |

|                                   | REQSEL           | DMA request                   |  |  |  |  |

| DMA Control Register              | ACKSEL           | DMA acknowledge               |  |  |  |  |

| Divia Control Register            | DMASTAT          | Early termination request     |  |  |  |  |

|                                   | DMACTL           | Early termination acknowledge |  |  |  |  |

### Table 11. Address Selector Types.

#### Selector

A Selector separately decodes read and write operations to the target address range, as shown in <u>Figure 9</u>. The RDSEL[1:0] output indicates a read operation, the WRSEL[1:0] output indicates a write operation.

#### **Chip Select**

A Selector in chip select mode decodes any read or write transaction to the target address range. <u>Figure 10</u> shows a functional drawing of a chip select function. The SEL[1:0] performs like a chip-select function, decoding both read and write transactions. The

RDSEL[1:0] output is asserted only during read operations and indicates the direction of a data transfer.

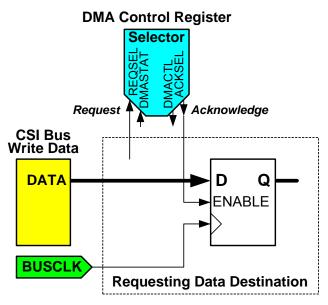

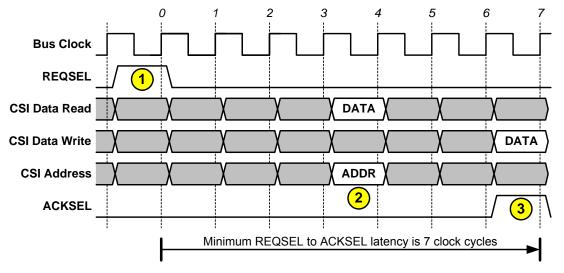

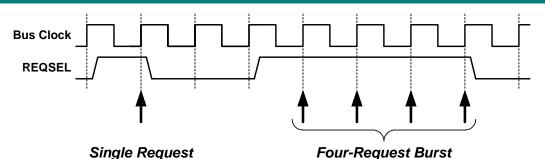

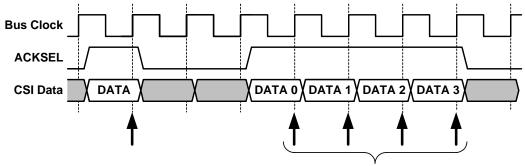

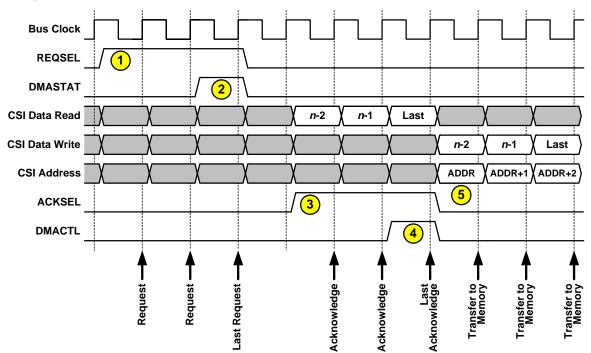

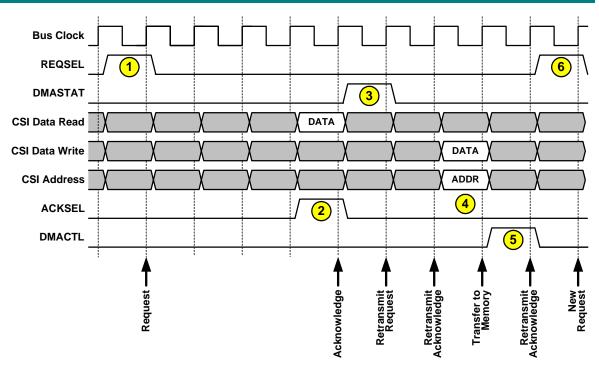

## DMA Control Register

A Selector provides a relocatable control register for CSL-based I/O devices requiring DMA access. The <u>DMA Control Register</u> enables requests and steers the request and acknowledge signals to the selected DMA channel. See the <u>DMA Controller</u> section for more information.

#### Data Access and Selectors Required

In a 32-bit system, data is optionally accessed as a single 32-bit word, two 16-bit halfwords, or as four individual bytes. Each Selector provides two write-enable outputs and two read-enable outputs to decode bus transactions to a specific address. The number of Selectors to decode a CSL-based function depends on the data width of the function and how it is accessed, as shown in <u>Table 12</u>.

For example, if the CSL-based function is a 32-bit wide register, then the CPU may access it as a word, a half-word, or a byte. If the application always accesses the CSL register as a word, never as a half-word or byte, then only half the Selector's outputs are required to decode the register. However, if the CPU accesses the 32-bit register as four bytes, then two Selectors are required.

| Function               | Data Access Type |           |      |  |  |  |

|------------------------|------------------|-----------|------|--|--|--|

| Data Width             | Word             | Half-Word | Byte |  |  |  |

| Word<br>(32 bits)      | 1/2              | 1         | 2    |  |  |  |

| Half-Word<br>(16 bits) | 1⁄2              | 1/2       | 1    |  |  |  |

| Byte<br>(8 bits)       | 1/2              | 1/2       | 1/2  |  |  |  |

# Table 12. Number of Selectors required to access a CSL-based function of a given data width, depending on data access type.

# CSI-to-CSL Bus Interface Design Example

Figure 11 illustrates how a 32-bit read/write register, implemented in the CSL logic, connects to the CSI bus socket. Physically, the 32-bit register requires 32 CSL cells. Because a CSL bank is just 16 CSL cells high, a 32-bit register requires two CSL banks, but is just one column wide. The actual physical implementation may be different, depending on the application.

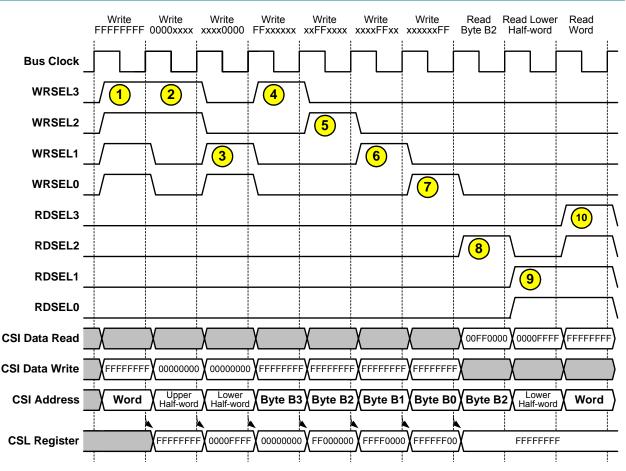

The CPU might access the 32-bit register as a 32-bit word, as two 16-bit half-words, or as four individual bytes, as shown in Figure 12. Consequently, a 32-bit register may require up to two address Selectors, which provide four separate read and write byte-enables. The number of Selectors required depends on the data width of the CSL-based function and the desired data access types, as shown in Table 12.

The signals shown in <u>Figure 12</u> are relative to the CSL side of the CSI bus socket. In this idealized series of transfers, the CPU performs various write and read transactions to the CSL-based register.

① The CPU writes 0xFFFFFFF as a word-wide transfer to the data register. All four byte-enables are asserted by their respective Selectors. The data register captures the value 0xFFFFFFFF on the next clock edge.

# Figure 11. A possible physical implementation of a 32-bit read/write data register connected to the CSI bus.

- ② The CPU writes 0x0000 to the upper half-word of the data register. The CSI bus automatically duplicates the upper half-word onto the lower half-word of the CSI Data Write bus, making the bus value 0x00000000. Only the two byte-enables controlling the upper 16 bits of the register are asserted. The data register captures the data and the register output becomes 0x0000FFFF on the next clock edge.

- ③ The CPU writes 0x0000 to the lower half-word of the data register. As before, the CSI bus automatically duplicates the half-word on the CSI Data Write bus. Only the two byte-enables controlling the lower 16 bits of the register are asserted. The data register captures the data and the register output becomes 0x0000000 on the next clock edge.

Figure 12. Idealized data transfers to a 32-bit register shown in Figure 11.

④ The CPU writes 0xFF to the upper-most byte, byte B3, of the data register. The CSI bus automatically duplicates the byte across all four byte lanes, making the CSI Data Write bus 0xFFFFFFFF. Only a single byte-enable is asserted, controlling the upper 8 bits of the register. The data register captures the data and the register output becomes 0xFF000000 on the next clock edge.

$\odot$  through  $\odot$  are similar to  $\circledast$  except that different byte-enables are asserted. After  $\oslash$ , the register value becomes 0xFFFFFFF on the next clock edge.

- In CPU reads from byte B2. Only the RDSEL2 byte-enable is asserted, placing bits Q[23:16] onto the CSI Data Read bus. All other byte lanes are zero because they are not selected in this transaction. The value 0x00FF0000 appears on the CSI Data Read bus.

- In CPU reads the lower half-word from the data register. The two byte-enables controlling the lower 16 bits of the register place bits Q[15:0] onto the CSI Data Read bus and the value 0x0000FFFF is captured on the next rising clock edge. All other byte lanes are zero.

- The CPU reads the entire 32-bit data register as a word-wide transaction. All four byte-enables are active placing bits Q[31:0] onto the CSI Data Read bus. The 0xFFFFFFF value is captured on the next rising clock edge.

#### Wait-State Monitor and Control Signals

The CSI socket interface includes signals to monitor and control wait-states on the internal system bus.

#### WAITED (output from bus socket)

The WAITED signal indicates that a wait-state was asserted during the previous CSI bus cycle. Though rarely used, this signal is typically used in FIFO control logic.

#### Initial Wait-State Insertion

Some CSL logic functions implemented in the CSL matrix may require wait-states, either because the CSL logic function handshakes with another asynchronous device or if the CSL logic function is too slow to respond in a single bus cycle.

If a CSL logic function requires *any* wait-states, then a Selector must assert the first waitstate. The Selector only asserts a wait-state if the system is accessing the Selector's target address space.

Should a CSL logic function require additional wait-states beyond the first wait-state asserted by the selector, then the CSL logic function inserts additional wait-states by asserting the WAITNEXT signal on the CSI socket interface.

If a CSL-based function requires any CSI bus wait-states, then a Selector must assert the first wait-state cycle.

### WAITNEXT (input to bus socket)

If a CSL function requires more than one wait-state, then it inserts additional wait-states by asserting the WAITNEXT signal before the next rising clock edge on Bus Clock. Again, a Selector must always insert the first wait-state. When valid on a rising clock edge, the WAITNEXT signal causes a wait-state on the next bus cycle.

A CSL-based function may insert any number of wait-states. There is not built-in time-out mechanism. Functions that insert wait-states while waiting for an external event should always consider the case where the external event never happens and release the bus.

#### **Breakpoint Event Monitor and Control Signals**

The CSI socket interface includes signals to monitor and control hardware breakpoint events. These signals can be used to aid system-level debugging.

#### EVENT (output from bus socket)

CSL functions can monitor hardware breakpoint events using the EVENT signal. When EVENT is asserted, a hardware breakpoint event has occurred, either caused by the builtin hardware breakpoint unit or by another function in the CSL matrix that asserted the BREAK signal.

The EVENT signal allows a CSL-based function to freeze in conjunction with the remainder of the system. A function that uses Bus Clock as its clock source is automatically frozen during a breakpoint event.

#### BREAK (input to bus socket)

CSL functions can force a hardware breakpoint event by asserting the BREAK signal. The built-in hardware breakpoint unit typically only monitors transactions on the CSI bus. The BREAK signal allows CSL functions to interact with the hardware breakpoint unit. For example, a CSL function could be monitoring a serial communications stream that rarely interacts with the system bus. Upon detecting a particular pattern or error condition, the CSL function could force a breakpoint event, stopping the system. The state of the system or CSL functions could then be monitored through the JTAG port.

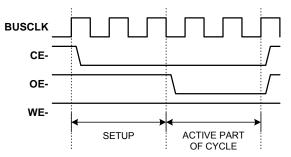

## **CSI Bus Transactions**

The following section provides some example CSI bus transactions, demonstrating the interaction of a CSL logic function and the CSI bus socket, including wait-states.

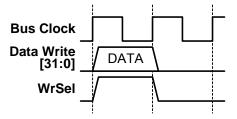

### Data Write Transactions

During a data write transaction, the system sends data to a CSL logic function. The system presents both write data and address.

Figure 13 shows a single-cycle write transaction to a CSL logic function. Write data and address are presented on the CSI socket interface. The address is decoded using a Selector. If the transaction is to the Selector's address range, then the Selector asserts its WRSEL signal. The CSL function uses WRSEL to enable a register, as shown in Figure 11, and captures the write data on the next rising clock edge.

### Figure 13. A single-cycle write transaction to a CSL logic function.

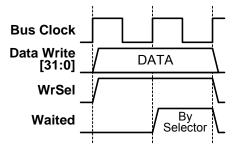

Figure 14 demonstrates a similar transaction, except that the CSL logic function requires two clock cycles to capture the write data. The CSL logic function's Selector is configured to assert the initial wait-state. When the Selector detects that the system is addressing it, it asserts its WRSEL signal and automatically asserts the initial wait-state.

During the wait-state, the bus master continues presenting write data and address and the Selector continues to assert its WRSEL output. The CSL function will capture the write data during the second bus cycle so it does not assert WAITNEXT. The WAITED signal indicates the wait-state inserted by the Selector during the first bus cycle. The transaction ends after the second bus cycle and the Selector de-asserts its WRSEL output.

#### Figure 14. A two-cycle write transaction to a CSL logic function.

See the "Designing with Triscend Selectors" technical document within FastChip for additional information on creating custom logic functions that connect to the CSI bus.

#### Data Read Transactions

During a data read transaction, the system presents the read address and the targeted CSL function presents the data.

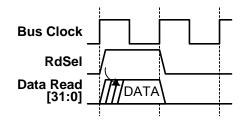

<u>Figure 15</u> shows a single-cycle read transaction from a CSL function. The read address is presented on the CSI socket interface. The address is decoded using a Selector. If addressed, then the Selector asserts its RDSEL signal. The CSL function uses RDSEL to enable data onto the Data Read output port on the CSI socket, as shown in <u>Figure 11</u>.

#### Figure 15. A single-cycle read transaction from a CSL logic function.

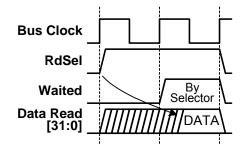

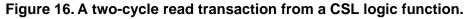

Figure 16 demonstrates a similar transaction, except that the CSL logic function requires two clock cycles to provide the read data. The CSL logic function's Selector is configured to assert the initial wait-state. When the Selector detects that the system is addressing it, it asserts its RDSEL signal and automatically asserts the initial wait-state.

During the wait-state, the bus master continues presenting address and the Selector continues to assert its RDSEL output. The CSL function will present valid read data during the second bus cycle so it does not assert WAITNEXT. The WAITED signal indicates the wait-state inserted by the Selector during the first bus cycle. The transaction ends after the second bus cycle and the Selector de-asserts its RDSEL output.

#### Using WAITNEXT during a transaction

There are four general rules for asserting a CSI bus wait-state, depending on the CSL function's response time.

- 1. If the CSL logic function can respond within a single bus cycle, the no wait-states are required.

- 2. If the CSL logic function can respond by the second bus cycle, then it associated Selector must insert a single wait-state.

- 3. If three or more bus cycles are required before the CSL logic function can respond, then the Selector is configured to insert the initial wait-state and the CSL function must insert additional wait-states using the WAITNEXT signal.

4. If any wait-states are required on one side of a transaction, either read or write, then the other side of the transaction requires at least one wait-state. The initial wait-state inserted by a Selector occurs on both read and write transactions.

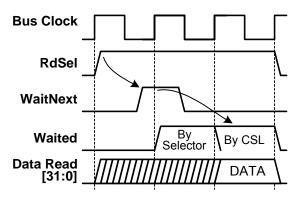

Figure 17 shows an example transaction where the selected CSL function insert waitstates using the WAITNEXT signal. During the first bus cycle, the addressed CSL function's Selector asserts it RDSEL output. In this example, the function always requires at least one wait-state, so the Selector inserts the initial wait-state. The CSL function is not ready to respond in the first bus cycle, so the function asserts WAITNEXT, inserting a wait state during the next bus cycle.

During the second bus cycle, the system continues providing address and the Selector continues asserting RDSEL. The CSL function determines that it is ready to respond during the next bus cycle and de-asserts WAITNEXT. The WAITED signal shows the wait-state inserted by the Selector during the first bus cycle.

Finally, during the third bus cycle, the CSL logic function is ready to respond. The CSL logic function provides data on the Read Data port on the CSI socket. The WAITED signal shows the wait-state inserted when the CSL function asserted WAITNEXT. The wait-state occurred on the second bus cycle but WAITED reports the wait-state on the following bus cycle.

Figure 17. A multi-cycle transaction using WAITNEXT to insert wait-states.

# **CSI Bus Arbiter**

The CSI bus arbiter schedules and manages traffic on the CSI bus.

#### **Bus Masters**

There are up to ten independent bus masters on the CSI bus, as shown below. Each DMA channel separately requests read and write transactions because these requests can sometimes be combined with other transfers on the CSI bus, as discussed below.

- 1. ARM7TDMI CPU 7. DMA 2 Read

- 2. JTAG unit 8. DMA 2 Write

- 3. DMA 0 Read 9. DMA 3 Read

- 4. DMA 0 Write 10. DMA 3 Write

- 5. DMA 1 Read

- 6. DMA 1 Write

#### Arbitration Scheme

All active bus masters arbitrate for the bus using a round-robin arbitration scheme with fixed prioritization. The arbitration priority rotates between the various active bus masters. The bus arbiter attempts to fully utilize the CSI bus bandwidth by intermixing non-conflicting transactions, as discussed below.

#### Simultaneous Transactions

The CSI bus arbiter can schedule two transactions during the same bus cycle provided that ...

- Of the two bus requests, only one transfer is to a memory-mapped location. There is only one address bus.

- The two transfer requests are in opposite directions. In other words, one must be a read transfer, the other a write transfer. There are separate read and write busses.

<u>Table 13</u> shows the type of traffic carried over the CSI bus and which portions of the CSI bus are used during each type of transaction. The conditions outlined above allow a variety of simultaneous transactions. For example, the CPU can write to a memory location while a DMA channel acknowledges a read request and gathers data from a CSL-based device.

|                                           | CSI Bus      |              |              |

|-------------------------------------------|--------------|--------------|--------------|

| Transaction Type                          | Address      | Read Data    | Write Data   |

| CPU Read Cycle (over CSI-to-local bus     | 1            | ✓            |              |

| bridge)                                   | -            | -            |              |

| CPU Write Cycle (over local-to-CSI bus    | 1            |              | 1            |

| bridge)                                   | •            |              | •            |

| DMA Acknowledge Read Cycle (read data     |              | <u>/</u>     |              |

| from device to DMA FIFO)                  |              | •            |              |

| DMA Acknowledge Write Cycle (write from   |              | · ·          |              |

| DMA FIFO to device)                       |              |              | v            |

| DMA Addressed Read Cycle (read from mem-  | 1            | 1            |              |

| ory to DMA FIFO)                          | •            | •            |              |

| DMA Addressed Write Cycle (write from DMA |              | · ·          |              |

| FIFO to memory)                           | × ·          |              | ¥            |

| JTAG Read Cycle                           | $\checkmark$ | $\checkmark$ |              |

| JTAG Write Cycle                          | $\checkmark$ |              | $\checkmark$ |

Table 13. CSI Bus Transaction Types.

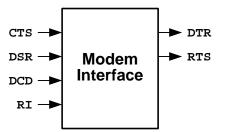

#### **Sideband Signals**

All of the signals on the CSI socket interface are designed to be processor independent. CSL logic functions designed using this interface can be re-used with future Triscend configurable system-on-chip families.

However, some signals are processor specific. The signals are called "sideband" signals. The sideband signals for the A7S family are shown in <u>Table 14</u>.

On most processors, these sideband signals would be assigned to dedicated pins. The A7S CSoC is more flexible and these signals are optionally routed to any available PIO pin or to logic in the CSL matrix.

|                                                                                 |                          |         | Active   |

|---------------------------------------------------------------------------------|--------------------------|---------|----------|

| A7S Function                                                                    | Direction                | Signal  | Polarity |

| Alternate clock, output of the phase-locked loop (PLL) multiplexer              | PLL → CSL                | ACLK    | High     |

| Phase-locked loop (PLL) lock indicator                                          | PLL → CSL                | Plock   | High     |

| System reset signal, <b>active-Low</b> . Active upon any system reset condition | Reset → CSL              | SysRstN | Low      |

| Serial port 0 transmit data                                                     | CSL → UART_0             | SOUT0   | High     |

| Serial port 1 transmit data                                                     | CSL → UART_1             | SOUT1   | High     |

| Serial port 0 baud rate clock                                                   | UART_0 $\rightarrow$ CSL | BDCLK0  | High     |

| Serial port 1 baud rate clock                                                   | UART_1 $\rightarrow$ CSL | BDCLK1  | High     |

| Modem Data Terminal Ready (DTR) signal                                          | UART → CSL               | DTR     | High     |

| Modem Request to Send (RTS) signal                                              | UART → CSL               | RTS     | High     |

| Application reset from CSL matrix                                               | $CSL \rightarrow CPU$    | AppRst  | High     |

| ARM7 Fast Interrupt (FIQ) signal                                                | $CSL \rightarrow CPU$    | FIQ     | High     |

| ARM7 Interrupt Request 2 (IRQ2)                                                 | $CSL \rightarrow CPU$    | IRQ2    | High     |

| ARM7 Interrupt Request 1 (IRQ1)                                                 | $CSL \rightarrow CPU$    | IRQ1    | High     |

| ARM7 Interrupt Request 0 (IRQ0)                                                 | $CSL \rightarrow CPU$    | IRQ0    | High     |

| Serial port 0 receive data                                                      | UART_0 $\rightarrow$ CSL | SIN1    | High     |

| Serial port 1 receive data                                                      | UART_1 → CSL             | SIN2    | High     |

| Modem Clear to Send (CTS) signal                                                | CSL → UART               | CTS     | High     |

| Modem Data Set Ready (DSR) signal                                               | CSL → UART               | DSR     | High     |

| Data Carrier Detect (DCD)                                                       | CSL → UART               | DCD     | High     |

| Modem Ring Indicator (RI)                                                       | CSL → UART               | RI      | High     |

# Table 14. A7S Family Sideband Signals.

The sideband signals are available as global signal names within FastChip.

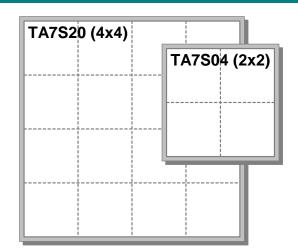

Figure 18. The two members of the A7S CSoC device family range in density from four CSL banks (448 CSL cells) up to 16 CSL banks (2,048 CSL cells).

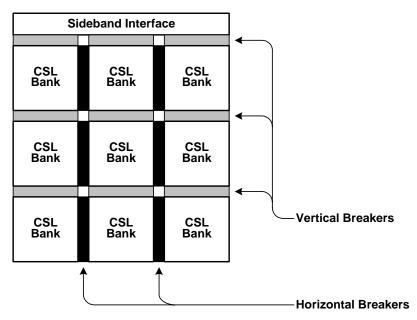

Figure 19. Vertical and horizontal breakers separate the individual CSL banks with Configurable System Interconnect (CSI) bus resources.

# Configurable System Logic (CSL)

The Configurable System Logic (CSL) matrix provides flexible, programmable resources to build almost any digital logic function. Because it is intimately connected to the CSI bus, the CSL matrix is ideal for building any custom peripherals or logic functions required by the CPU. The matrix consists of multiple CSL banks. Each bank is a rectangular array of individual CSL cells.

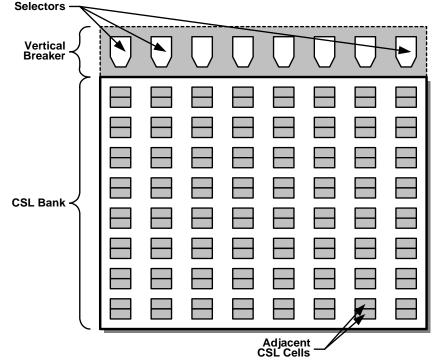

Figure 20. A CSL bank consists of multiple columns, each with 16 rows of CSL cells.

The number of CSL banks varies by part number. The highest-density A7S family device, the TA7S20, contains 16 CSL banks, arranged in a 4x4 array as shown in <u>Figure 18</u> and <u>Figure 20</u>. The smallest member, the TA7S04, has just four CSL banks, arranged in a 2x2 array.

|               | CSL Cells Per Bank |      |                    | Banks Per Device |      |                |                    |

|---------------|--------------------|------|--------------------|------------------|------|----------------|--------------------|

| Device        | Columns            | Rows | CSL Cells/<br>Bank | Columns          | Rows | Total<br>Banks | Total<br>CSL Cells |

| <b>TA7S04</b> | 7                  | 16   | 112                | 2                | 2    | 4              | 448                |

| <b>TA7S20</b> | 8                  | 16   | 128                | 4                | 4    | 16             | 2,048              |

Table 15. CSL Banks by Device.

Vertical and horizontal breakers separate the individual CSL banks on a device, as shown in <u>Figure 19</u>. Vertical breakers appear at the top of every CSL bank. Horizontal breakers appear between adjacent columns of CSL banks. The breakers contain Configurable System Interconnect (CSI) bus resources. The horizontal breakers distribute CSI bus address signals to the CSL banks. The vertical breakers distribute the Selector input and output signals, breakpoint control signals, the global buffer signals, and the wait-state control signals. The CSI read data return path is also located in the vertical breakers.

Signals from one CSL bank can cross into other banks via the breakers, though crossing a breaker adds delay to the signal.

Sideband signals originate and terminate in resources along the top edge of the device.

#### Bank Resources

Each CSL bank consists of multiple columns, each with 16 rows of CSL cells. Figure 20 shows the basic layout of the cells within a bank. Pairs of adjacent CSL cells share resources to build more complex cell functions. The Selectors, located in the vertical breaker above the bank, distribute any decoded address signals. There is one address Selector per column of 16 CSL cells.

Programmable interconnect surrounds the CSL cells. These programmable "wires" allow a signal originating from one CSL cell to communicate with one or more CSL cells, even those in other CSL banks. Likewise, signals to and from the CSI bus are distributed to and from individual CSL cells.

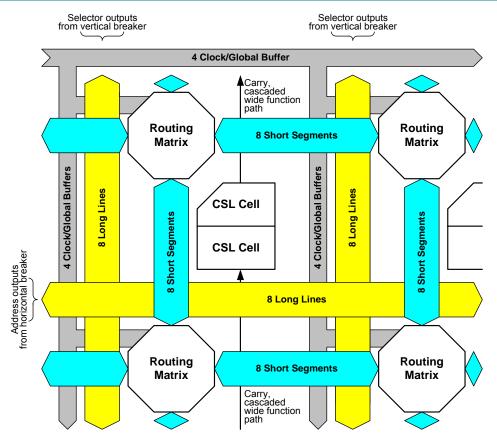

#### General-purpose Interconnect

The general-purpose interconnect, shown in <u>Figure 22</u>, distributes signals within a CSL bank. Metal lines of various lengths and purposes connect to individual CSL cells, to the horizontal and vertical breakers, and to the distributed array of routing matrices. Each routing matrix provides connections between the various lines entering or exiting the segment. The various interconnect resources are described below.

- 8 Short Segment lines in each vertical and horizontal channel, connecting adjacent routing matrices.

- 8 Long Lines in each vertical and horizontal channel. These long lines traverse the width or breadth of the CSL bank. The vertical long lines optionally distribute the outputs from the Selectors located in the vertical breaker. The horizontal long lines optionally distribute address signals from CSI bus.

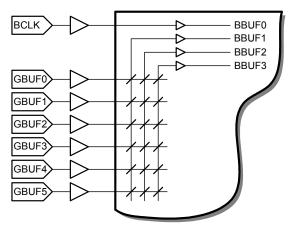

- Bus clock and 3 of 6 global buffer signal lines in every vertical channel, as shown in Figure 21. The bus clock signal is distributed globally to all resources on an A7S CSoC device. Within a CSL bank, any three of the six global buffer signals are available.

- A carry/cascade signal between adjacent pairs of CSL cells, for faster arithmetic functions and for wide logic functions.

Figure 21. The bus clock signal and any 3 of the 6 global buffer signals are available within a CSL bank.

Figure 22. The general-purpose interconnect surrounds a pair of adjacent CSL cells.

Figure 23. CSI bus write data is available at each routing matrix. Read data returns to the CSI bus.

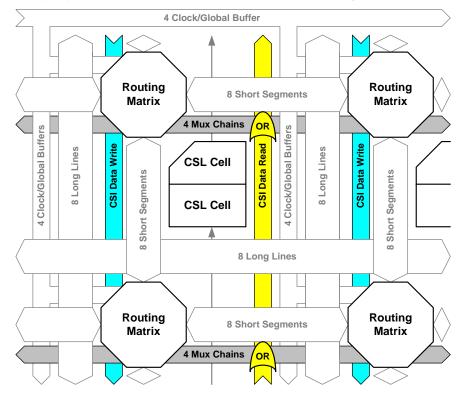

### CSI Bus Read and Write Data Distribution

Beyond the general-purpose signals, the programmable interconnect also distributed data signals to and from the CSI bus, as shown in <u>Figure 23</u>.

- CSI Write Data is accessible at every routing matrix, distributed throughout the CSL bank.

- 4 Multiplexer Chains for distributing bi-directional data across a CSL bank. The multiplexer chains behave much like a bi-directional, three-state bus but avoids the potential data-contention problems and associated power consumption of a three-state bus because all signals are unidirectional.

- CSI Read Data paths gather the values of individual data lines from throughout the device. Ultimately, all the signals return to the CSI bus. The signals from individual bit lines are gathered via an OR-chain.

#### Signal-Flow Directional Preferences

Though the interconnect was designed to minimize directionality, there are few inherent preferences inspired by the architecture, as shown in <u>Figure 24</u>.